為了贏得技術(shù)領(lǐng)導(dǎo)地位的競(jìng)爭(zhēng),以及半導(dǎo)體賦能的關(guān)鍵行業(yè),例如人工智能、高性能計(jì)算、先進(jìn)通信、量子、能源、國(guó)防、醫(yī)療技術(shù)和交通運(yùn)輸,美國(guó)必須重新鞏固其作為半導(dǎo)體創(chuàng)新中心的地位。根據(jù)《2021財(cái)年國(guó)防授權(quán)法案》設(shè)立并由《芯片與科學(xué)法案》資助的聯(lián)邦研究項(xiàng)目,正在努力應(yīng)對(duì)該行業(yè)、其技術(shù)以及最重要的創(chuàng)新運(yùn)作方式的不斷變化的特性。這些投資正開始彌補(bǔ)美國(guó)半導(dǎo)體競(jìng)爭(zhēng)力、韌性和供應(yīng)鏈安全方面的具體差距。而且,這些投資是在行業(yè)劇烈變革正在重新調(diào)整創(chuàng)新格局的關(guān)鍵時(shí)刻進(jìn)行的。

關(guān)鍵要點(diǎn)

1

為了贏得全球技術(shù)領(lǐng)導(dǎo)地位的競(jìng)爭(zhēng),美國(guó)必須保持其在半導(dǎo)體創(chuàng)新領(lǐng)域的領(lǐng)先地位。

2

CHIPS 研發(fā)項(xiàng)目有潛力實(shí)施一項(xiàng)積極、全面且與行業(yè)保持一致的戰(zhàn)略,該戰(zhàn)略反映了行業(yè)最新的創(chuàng)新軌跡。

3

這些項(xiàng)目在向獲獎(jiǎng)?wù)卟渴鹳Y源方面取得了進(jìn)展,其中多個(gè)項(xiàng)目目前正在進(jìn)行中。這些項(xiàng)目已開始開發(fā)所需的基礎(chǔ)設(shè)施,小型場(chǎng)地和大型設(shè)施的最終合同已簽訂,目前正在進(jìn)行合同談判。需要取得更多進(jìn)展,以制定符合行業(yè)優(yōu)先事項(xiàng)和大批量生產(chǎn)需求的研究議程,并開始實(shí)施該議程。

4

隨著這些項(xiàng)目的持續(xù)實(shí)施,它們必須維持在適當(dāng)?shù)乃剑⒈3謱?duì)以行業(yè)為導(dǎo)向的規(guī)劃的承諾。

加大研發(fā)投入,應(yīng)對(duì)日益激烈的創(chuàng)新領(lǐng)導(dǎo)力競(jìng)爭(zhēng)

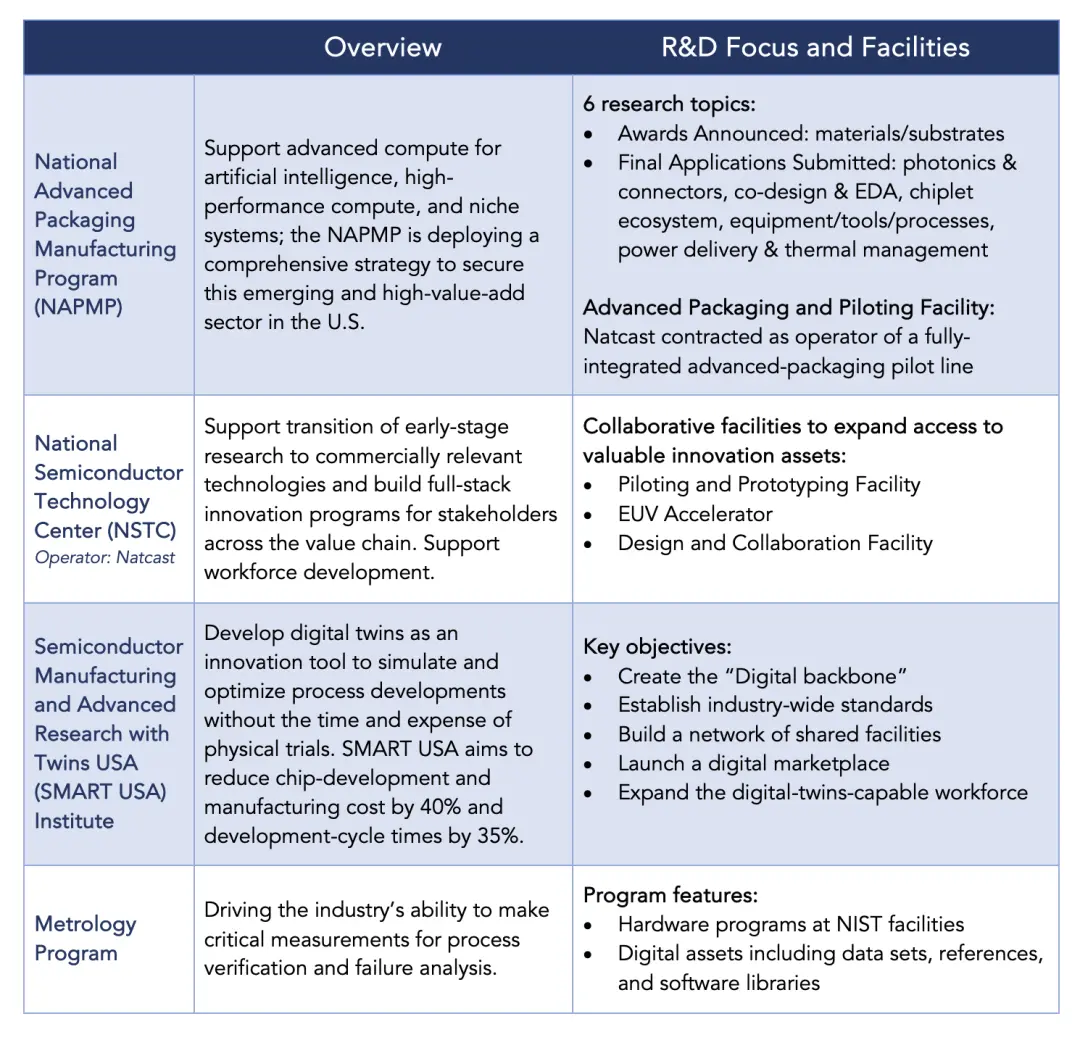

近年來,世界各國(guó)政府——無論是盟國(guó)還是競(jìng)爭(zhēng)對(duì)手——都在為爭(zhēng)奪先進(jìn)的半導(dǎo)體研發(fā)資源展開激烈競(jìng)爭(zhēng),因?yàn)樗麄兩钪舛搜芯康拈_展地決定了最尖端企業(yè)的增長(zhǎng)地。聯(lián)邦政府通過芯片研發(fā)辦公室(CRDO)資助的半導(dǎo)體研究項(xiàng)目,承諾實(shí)施一項(xiàng)雄心勃勃、全面且與行業(yè)協(xié)調(diào)一致的戰(zhàn)略,以確保最尖端的半導(dǎo)體技術(shù)在美國(guó)開發(fā)、在美國(guó)制造,并造福美國(guó)經(jīng)濟(jì)。CRDO項(xiàng)目正在使這些創(chuàng)新資產(chǎn)的獲取更加民主化,而如果沒有公共資金,這些資產(chǎn)將無法獲得。本文回顧的CRDO項(xiàng)目如下:

研發(fā)投資將長(zhǎng)期保持美國(guó)制造業(yè)領(lǐng)先地位

芯片研發(fā)項(xiàng)目 (CHIPS) 是對(duì)美國(guó)國(guó)內(nèi)半導(dǎo)體制造產(chǎn)能 5400 億美元投資的重要補(bǔ)充。過去,該行業(yè)的產(chǎn)品周期以兩年為一個(gè)周期。然而,隨著行業(yè)向新型創(chuàng)新戰(zhàn)略轉(zhuǎn)型,產(chǎn)品周期正在加速。美國(guó)必須贏得全球半導(dǎo)體創(chuàng)新核心的競(jìng)爭(zhēng),才能保持這些國(guó)內(nèi)設(shè)施長(zhǎng)期處于領(lǐng)先地位。此外,核心研發(fā)與發(fā)展辦公室 (CRDO) 項(xiàng)目的行業(yè)驅(qū)動(dòng)性質(zhì)旨在支持美國(guó)半導(dǎo)體供應(yīng)鏈的持續(xù)振興,這與政府提升美國(guó)創(chuàng)新和制造競(jìng)爭(zhēng)力的優(yōu)先事項(xiàng)相一致。此外,與旨在投資早期技術(shù)的傳統(tǒng)政府資助項(xiàng)目不同,CRDO 項(xiàng)目肩負(fù)著獨(dú)特的使命,即在短期內(nèi)激活大規(guī)模生產(chǎn)所需的技術(shù)。

半導(dǎo)體研究項(xiàng)目的重要性

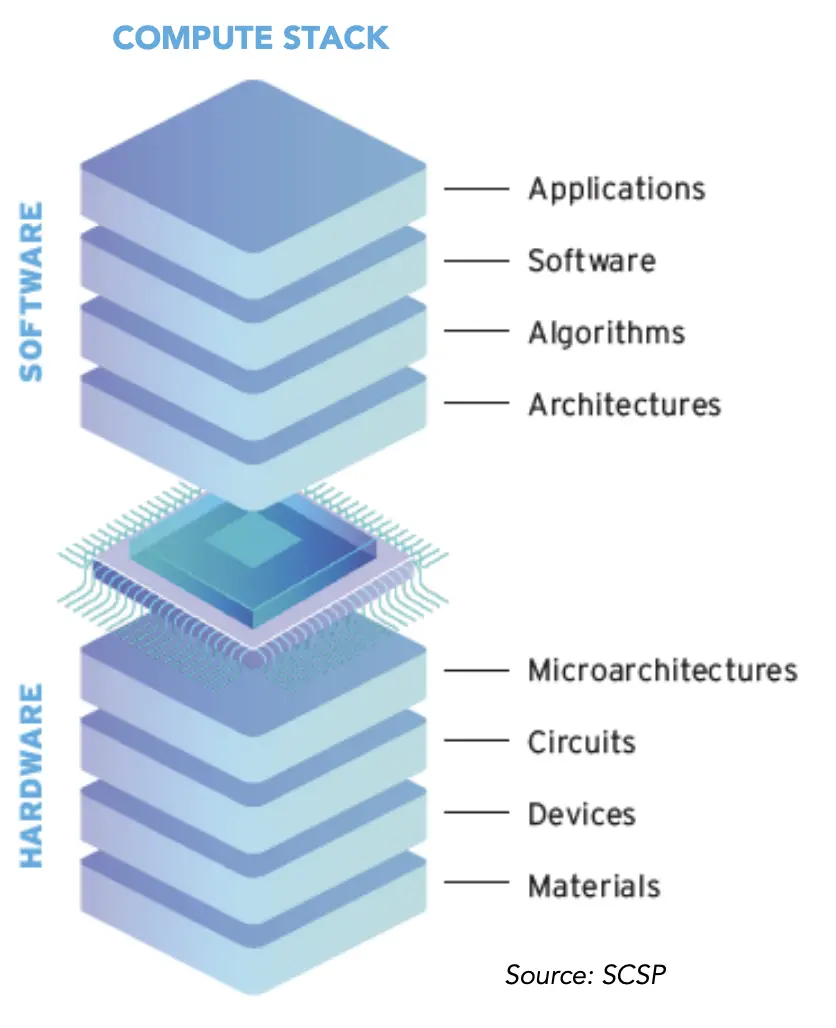

隨著這些研究項(xiàng)目的不斷推進(jìn),它們有望應(yīng)對(duì)半導(dǎo)體行業(yè)面臨的創(chuàng)新挑戰(zhàn),并推動(dòng)整個(gè)計(jì)算堆棧的進(jìn)步。

一、摩爾定律及未來發(fā)展趨勢(shì)

近年來,半導(dǎo)體創(chuàng)新的全新途徑層出不窮,需要新的合作和技術(shù)開發(fā)方法。在過去的幾十年里,計(jì)算性能的提升主要通過“微縮”來實(shí)現(xiàn)——將芯片上的功能最小化,以便在單個(gè)硅片上容納更多晶體管。因此,“摩爾定律”預(yù)測(cè),芯片上的晶體管數(shù)量將每?jī)赡攴环瑫r(shí)成本也會(huì)下降。幾十年來,這種創(chuàng)新模式取得了顯著的成果,摩爾定律的步伐至今仍在繼續(xù)。然而,新的創(chuàng)新前沿為先進(jìn)邏輯、存儲(chǔ)器和模擬器件的計(jì)算性能的飛躍發(fā)展帶來了巨大的希望。這些新方法超越了摩爾定律,并呼吁“全棧”戰(zhàn)略——在軟件、材料、設(shè)計(jì)、架構(gòu)和封裝方面進(jìn)行創(chuàng)新——并要求整個(gè)價(jià)值鏈的協(xié)作。同時(shí),對(duì)于越來越多的應(yīng)用(例如工業(yè)、醫(yī)療設(shè)備、汽車等領(lǐng)域的某些終端用途),性能不再僅僅由晶體管的數(shù)量來衡量;相反,新的解決方案為新的終端市場(chǎng)帶來了新的價(jià)值主張,例如超低功耗、高帶寬、在更高電壓下工作的能力、在更高溫度下更高的穩(wěn)定性或更低的延遲。

二、聯(lián)邦投資助力創(chuàng)新

客戶的新需求正在重新定位和拓展半導(dǎo)體行業(yè)的創(chuàng)新方式,而芯片研發(fā)項(xiàng)目 (CHIPS) 旨在提供必要的基礎(chǔ)設(shè)施和協(xié)作研究平臺(tái),以確保美國(guó)半導(dǎo)體生態(tài)系統(tǒng)在各個(gè)創(chuàng)新維度上保持領(lǐng)先于全球競(jìng)爭(zhēng)對(duì)手。

作為聯(lián)邦政府支持的研究項(xiàng)目的補(bǔ)充,這些新項(xiàng)目填補(bǔ)了美國(guó)半導(dǎo)體生態(tài)系統(tǒng)的空白,允許激烈的行業(yè)競(jìng)爭(zhēng)對(duì)手在競(jìng)爭(zhēng)前的協(xié)作空間中共同應(yīng)對(duì)重要的創(chuàng)新需求。

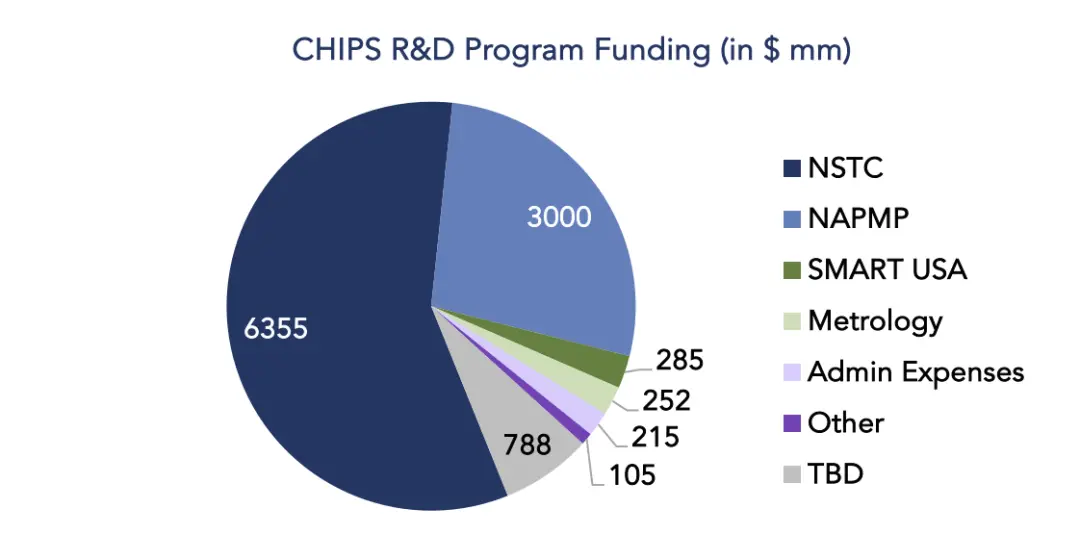

這些項(xiàng)目框架以行業(yè)領(lǐng)袖和技術(shù)路線圖為指導(dǎo),使國(guó)家應(yīng)用關(guān)鍵技術(shù)項(xiàng)目 (NAPMP)、國(guó)家科學(xué)技術(shù)委員會(huì) (NSTC)、美國(guó)智能技術(shù)與創(chuàng)新計(jì)劃 (SMART USA) 和計(jì)量學(xué) (Metrology) 能夠?yàn)閲?guó)家?guī)砭薮蠖焖俚挠绊懀瑫r(shí)確保美國(guó)在未來的技術(shù)競(jìng)賽中領(lǐng)先于全球競(jìng)爭(zhēng)對(duì)手。這些項(xiàng)目的資金總額約為110億美元,五年分配如下:

為了在全球半導(dǎo)體創(chuàng)新競(jìng)賽中有效競(jìng)爭(zhēng),這些項(xiàng)目必須維持在適當(dāng)?shù)乃健>S持適當(dāng)?shù)馁Y金水平將確保這些項(xiàng)目擁有足夠的資源開展工作,并與行業(yè)合作伙伴建立牢固的聯(lián)系。

三、芯片研發(fā)項(xiàng)目概述

美國(guó)商務(wù)部管理的四個(gè)項(xiàng)目旨在滿足美國(guó)半導(dǎo)體行業(yè)不斷發(fā)展的技術(shù)發(fā)展需求。這些項(xiàng)目在編制過程中充分考慮了行業(yè)的意見,而持續(xù)的行業(yè)洞察對(duì)于確保這些項(xiàng)目始終與行業(yè)合作伙伴保持密切聯(lián)系至關(guān)重要。這些項(xiàng)目概述如下,更多詳細(xì)信息請(qǐng)參閱本報(bào)告的其余部分。

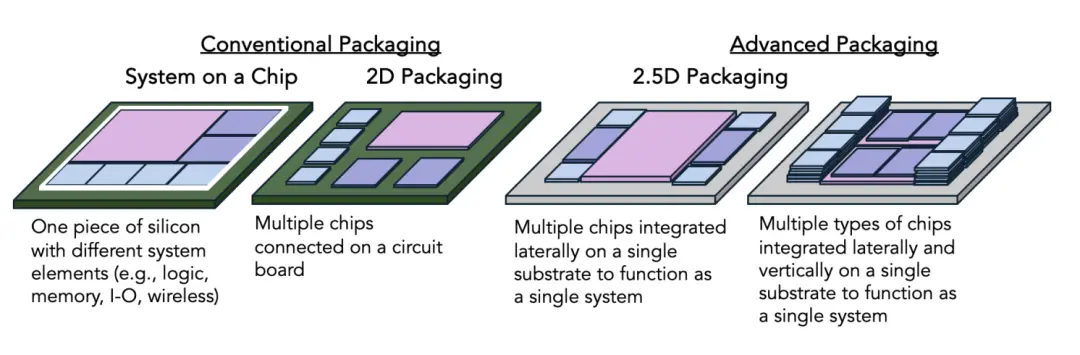

通過先進(jìn)封裝技術(shù)進(jìn)行創(chuàng)新

先進(jìn)封裝是一種新型半導(dǎo)體技術(shù),有望加速人工智能和高性能計(jì)算(AI 和 HPC)領(lǐng)域最強(qiáng)大芯片的性能提升。它還將促進(jìn)更快速、更經(jīng)濟(jì)地設(shè)計(jì)和制造可定制系統(tǒng),以滿足高混合、小批量市場(chǎng)的需求,例如對(duì)國(guó)家安全至關(guān)重要的國(guó)防應(yīng)用。過去,最先進(jìn)的芯片性能受限于單個(gè)二維硅片(即“系統(tǒng)級(jí)芯片”,SOC)上能夠?qū)崿F(xiàn)的功能。

現(xiàn)在,先進(jìn)封裝技術(shù)使芯片系統(tǒng)的各個(gè)組件能夠單獨(dú)制造,然后再集成到單個(gè)封裝中,最終提高整個(gè)芯片的總硅含量(從而提高計(jì)算能力)。傳統(tǒng)封裝不會(huì)直接影響芯片性能,而先進(jìn)封裝如今已成為提升計(jì)算性能的關(guān)鍵手段。此外,通過分別制造芯片的不同組件,晶圓廠能夠簡(jiǎn)化制造流程,提高工廠產(chǎn)量和良率,并實(shí)現(xiàn)更持續(xù)的創(chuàng)新和產(chǎn)品改進(jìn),因?yàn)橄到y(tǒng)的所有組件不再需要一起設(shè)計(jì)和制造,從而提高盈利能力。

雖然最早的先進(jìn)封裝技術(shù)現(xiàn)已投入商業(yè)市場(chǎng),但其大部分潛力仍未顯現(xiàn)——而這一關(guān)鍵領(lǐng)域的全球領(lǐng)導(dǎo)地位也懸而未決。美國(guó)目前面臨著封裝供應(yīng)鏈的嚴(yán)重短缺,其組裝、測(cè)試和封裝產(chǎn)能僅占全球的4%。鑒于先進(jìn)封裝在推動(dòng)計(jì)算性能方面的作用即將上升,現(xiàn)在正值美國(guó)大力發(fā)展先進(jìn)封裝,并抓住這個(gè)不斷增長(zhǎng)的高附加值領(lǐng)域,為美國(guó)培育產(chǎn)能的絕佳戰(zhàn)略時(shí)機(jī)。

美國(guó)國(guó)會(huì)認(rèn)識(shí)到半導(dǎo)體封裝創(chuàng)新的重要性,并設(shè)立了國(guó)家先進(jìn)封裝制造計(jì)劃 (NAPMP),旨在“加強(qiáng)國(guó)內(nèi)生態(tài)系統(tǒng)中半導(dǎo)體先進(jìn)測(cè)試、組裝和封裝能力”(15 U.S.C. 4656(d))。該計(jì)劃由美國(guó)國(guó)家標(biāo)準(zhǔn)與技術(shù)研究院 (NIST) 牽頭,重點(diǎn)關(guān)注對(duì)公眾利益至關(guān)重要的封裝應(yīng)用,即人工智能 (AI) 和高性能計(jì)算 (HPC)。NAPMP 正在與其他項(xiàng)目(包括美國(guó)國(guó)防部高級(jí)研究計(jì)劃局 (DARPA) 的下一代微電子制造計(jì)劃)進(jìn)行廣泛協(xié)調(diào),以投資半導(dǎo)體和人工智能生態(tài)系統(tǒng)。

NAPMP 的使命是制定一項(xiàng)整體戰(zhàn)略,以解決這些緊迫的挑戰(zhàn),并促進(jìn)國(guó)內(nèi)先進(jìn)封裝產(chǎn)業(yè)的蓬勃發(fā)展。NAPMP 戰(zhàn)略圍繞六個(gè)已確定的研究領(lǐng)域構(gòu)建:

1. 材料與基板

2. 設(shè)備、工具與工藝

3. 電力輸送與熱管理

4. 光子學(xué)與連接器

5. 協(xié)同設(shè)計(jì)、EDA 及

6. Chiplet 生態(tài)系統(tǒng)

附錄一詳述了六個(gè)研發(fā)重點(diǎn)領(lǐng)域及其對(duì)半導(dǎo)體創(chuàng)新的重要性。截至2025年6月,NAPMP已敲定3億美元的資金用于其首個(gè)研發(fā)資助項(xiàng)目,重點(diǎn)關(guān)注材料和基板領(lǐng)域。此外,該項(xiàng)目還簽訂了一份價(jià)值11億美元的合同,用于建立其旗艦項(xiàng)目先進(jìn)封裝試點(diǎn)設(shè)施(APPF)。該設(shè)施將與位于亞利桑那州的國(guó)家技術(shù)中心(NSTC)試點(diǎn)設(shè)施共址并協(xié)同運(yùn)營(yíng)。業(yè)界也在熱切等待關(guān)于另外五個(gè)研發(fā)項(xiàng)目的資助決定,但最終的資助金額(總額達(dá)16億美元)尚未公布。

APPF將投資于集成制造先進(jìn)封裝工藝流程,以便新技術(shù)能夠在商業(yè)化的封裝規(guī)模上得到驗(yàn)證。在該設(shè)施中驗(yàn)證創(chuàng)新的可行性將大大降低技術(shù)開發(fā)過程中的風(fēng)險(xiǎn),并使其能夠更高效地集成到商業(yè)化的先進(jìn)封裝運(yùn)營(yíng)中。隨著 APPF 計(jì)劃的發(fā)展,需要與業(yè)界持續(xù)合作,以確保該設(shè)施成功建立強(qiáng)大的美國(guó)先進(jìn)封裝行業(yè)。

創(chuàng)新全半導(dǎo)體技術(shù)棧

半導(dǎo)體行業(yè)的創(chuàng)新日益強(qiáng)調(diào)協(xié)作,NSTC 旨在為整個(gè)美國(guó)半導(dǎo)體生態(tài)系統(tǒng)建立長(zhǎng)期的研發(fā)資源,使成熟的行業(yè)參與者、初創(chuàng)企業(yè)和學(xué)術(shù)界能夠在國(guó)內(nèi)取得廣泛成功。幾十年來,計(jì)算機(jī)硬件創(chuàng)新和計(jì)算機(jī)軟件創(chuàng)新一直處于相對(duì)獨(dú)立的循環(huán)中。硬件供應(yīng)商通過集成更多晶體管來制造更強(qiáng)大的處理器,而軟件供應(yīng)商則編寫程序來執(zhí)行客戶的計(jì)算工作負(fù)載。

如今,該行業(yè)嚴(yán)重依賴新的“全棧”解決方案,以便更好地定制硬件和軟件,最終交付性能和效率更高的集成系統(tǒng)。事實(shí)證明,這種創(chuàng)新策略是有效的,但它需要參與者在整個(gè)計(jì)算棧和整個(gè)價(jià)值鏈中加強(qiáng)協(xié)作。其他地區(qū)(例如歐洲、日本、中國(guó)臺(tái)灣、新加坡、中國(guó)大陸等)已大力投資國(guó)家半導(dǎo)體研究聯(lián)盟,以促進(jìn)此類創(chuàng)新,但美國(guó)的成功和進(jìn)步速度將取決于我們能否利用新的環(huán)境、工具和基礎(chǔ)設(shè)施在國(guó)內(nèi)擴(kuò)大協(xié)作創(chuàng)新規(guī)模。

NSTC 成立的宗旨是“開展先進(jìn)半導(dǎo)體技術(shù)的研究和原型設(shè)計(jì),并發(fā)展國(guó)內(nèi)半導(dǎo)體勞動(dòng)力隊(duì)伍,以增強(qiáng)國(guó)內(nèi)供應(yīng)鏈的經(jīng)濟(jì)競(jìng)爭(zhēng)力和安全性”(15 U.S.C. 4656(c))。國(guó)會(huì)指示 NSTC 以“公私合作聯(lián)盟”的形式運(yùn)作,私營(yíng)部門和聯(lián)邦研究機(jī)構(gòu)均參與其中。為了確保 NSTC 的長(zhǎng)期成功并獲得持續(xù)的行業(yè)支持,其運(yùn)作必須持續(xù)響應(yīng)行業(yè)技術(shù)優(yōu)先事項(xiàng)。

美國(guó)商務(wù)部指定 Natcast(美國(guó)國(guó)家半導(dǎo)體技術(shù)進(jìn)步中心)作為專門的非營(yíng)利組織,負(fù)責(zé)運(yùn)營(yíng) NSTC,并通過一項(xiàng)長(zhǎng)期資助協(xié)議提供 63 億美元資金。NSTC 的三大總體目標(biāo)是:

• 擴(kuò)大美國(guó)的技術(shù)領(lǐng)先地位;

• 減少原型設(shè)計(jì)和制造的時(shí)間和成本;

• 建立并維持半導(dǎo)體勞動(dòng)力發(fā)展生態(tài)系統(tǒng)。

作為公私合作項(xiàng)目,NSTC 的工作由美國(guó)商務(wù)部和由半導(dǎo)體供應(yīng)鏈各環(huán)節(jié)頂尖技術(shù)專家組成的專家技術(shù)顧問委員會(huì)共同指導(dǎo)。為了提供實(shí)現(xiàn)這些目標(biāo)所需的基礎(chǔ)設(shè)施,NSTC 正在建設(shè)三個(gè)主要設(shè)施,下文將簡(jiǎn)要介紹。更詳細(xì)的描述請(qǐng)參見附錄二。

1. 原型設(shè)計(jì)和先進(jìn)封裝試點(diǎn)設(shè)施:NSTC 致力于將新型制造和先進(jìn)封裝技術(shù)規(guī)模化,使其具備商業(yè)應(yīng)用價(jià)值,并促進(jìn)“實(shí)驗(yàn)室到工廠”的轉(zhuǎn)型。新技術(shù)通常始于學(xué)術(shù)界,并以小規(guī)模和低產(chǎn)量進(jìn)行演示。一旦概念驗(yàn)證完成,就必須開展大量的開發(fā)工作,使技術(shù)成熟,以便在商業(yè)市場(chǎng)中部署。事實(shí)上,如果不將晶圓送入完全集成的制造流程并測(cè)量其整體性能,就無法評(píng)估一項(xiàng)新技術(shù)的價(jià)值。原型設(shè)計(jì)和先進(jìn)封裝試點(diǎn)設(shè)施將為這一能力提供完整、集成的制造流程。該設(shè)施將位于亞利桑那州立大學(xué)研究園區(qū)。初步計(jì)劃于2026年在亞利桑那州立大學(xué)啟動(dòng),新設(shè)施將于2028年底竣工。

2. EUV加速器:極紫外 (EUV) 光刻技術(shù)已被證明是制造先進(jìn)半導(dǎo)體不可或缺的重要工具,EUV光刻技術(shù)(以及其繼任者高數(shù)值孔徑 (NA) EUV光刻技術(shù))的持續(xù)發(fā)展對(duì)于行業(yè)跟上尖端制造技術(shù)的發(fā)展至關(guān)重要。同時(shí),相關(guān)行業(yè)中支持光刻技術(shù)的領(lǐng)域也必須同步推進(jìn)其技術(shù)發(fā)展。國(guó)家半導(dǎo)體技術(shù)委員會(huì) (NSTC) EUV加速器的任務(wù)是讓這一重要工具的使用更加普及,并支持整個(gè)行業(yè)共同開發(fā)創(chuàng)新,更快地將新的EUV技術(shù)推向市場(chǎng)。該設(shè)施預(yù)計(jì)將于2025年夏季投入使用。

3.設(shè)計(jì)協(xié)作設(shè)施 (DCF:Design Collaboration Facility):確定晶圓上數(shù)十億個(gè)晶體管的布局以執(zhí)行大規(guī)模計(jì)算工作是一項(xiàng)極其復(fù)雜的任務(wù)。半導(dǎo)體價(jià)值鏈的設(shè)計(jì)環(huán)節(jié)包括開發(fā)電子設(shè)計(jì)自動(dòng)化 (EDA) 軟件的公司、組裝設(shè)計(jì)模塊庫(kù)以用于芯片設(shè)計(jì)的 IP 提供商,以及使用 EDA 軟件和 IP 模塊設(shè)計(jì)完整芯片系統(tǒng)的無晶圓廠公司。DCF 將支持設(shè)計(jì)研發(fā),并配備一個(gè)全新的“設(shè)計(jì)使能網(wǎng)關(guān)”,通過集中訪問 EDA 軟件和數(shù)據(jù)庫(kù),降低芯片初創(chuàng)企業(yè)的門檻。通過利用國(guó)家半導(dǎo)體技術(shù)委員會(huì) (NSTC) 及其成員的集體購(gòu)買力,DCF 將加快研發(fā)進(jìn)度,并顯著降低與實(shí)驗(yàn)芯片和架構(gòu)的設(shè)計(jì)和開發(fā)相關(guān)的不斷增長(zhǎng)的成本。該設(shè)施預(yù)計(jì)將于2025年夏季投入使用。

與其他旨在支持在《芯片法案》授權(quán)到期前到期的定期研究計(jì)劃的芯片研發(fā)項(xiàng)目不同,NSTC的使命和活動(dòng)旨在超越《芯片法案》,并長(zhǎng)期獲得私營(yíng)部門資金的支持。盡管在制定技術(shù)議程方面仍有大量工作要做,但NSTC正在啟動(dòng)長(zhǎng)期項(xiàng)目和架構(gòu),以在未來數(shù)十年內(nèi)成為半導(dǎo)體行業(yè)研究聯(lián)盟。

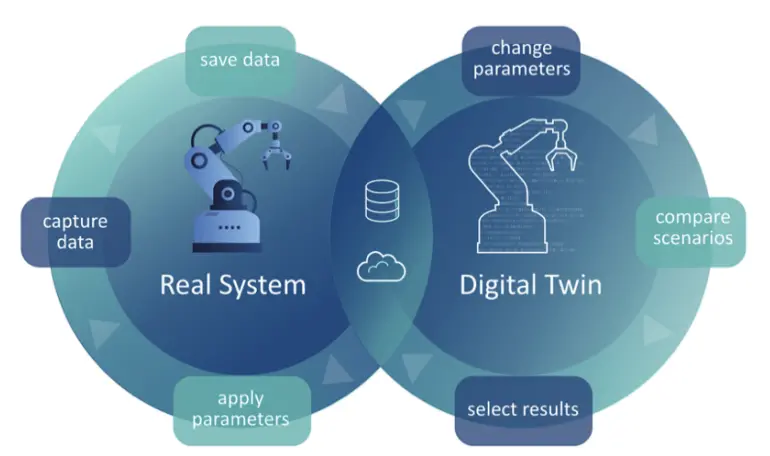

利用數(shù)字孿生技術(shù)創(chuàng)新

SMART USA(基于孿生技術(shù)的半導(dǎo)體制造高級(jí)研究機(jī)構(gòu))是一家新成立的美國(guó)制造業(yè)研究所,旨在推動(dòng)美國(guó)半導(dǎo)體產(chǎn)業(yè)價(jià)值鏈中的數(shù)字孿生技術(shù)發(fā)展。數(shù)字孿生是物理系統(tǒng)的虛擬表示,并保持實(shí)時(shí)連接。這種架構(gòu)使工程師能夠虛擬地(使用真實(shí)數(shù)據(jù)流)模擬和優(yōu)化流程,然后將結(jié)果直接應(yīng)用于物理系統(tǒng),而無需像物理試驗(yàn)?zāi)菢邮艿劫Y源密集度和時(shí)間限制。最終,數(shù)字孿生技術(shù)能夠賦能數(shù)字領(lǐng)域的更多創(chuàng)新,利用人工智能降低開發(fā)成本,并加速技術(shù)上市,領(lǐng)先于全球競(jìng)爭(zhēng)對(duì)手。

數(shù)字孿生可以在多個(gè)層面創(chuàng)建。單個(gè)制造步驟可以進(jìn)行孿生,以快速優(yōu)化晶圓加工條件。在更廣泛的層面上,可以對(duì)制造流程中的關(guān)鍵“層”(用于圖案化特征的少數(shù)相關(guān)步驟)進(jìn)行孿生,以了解如何協(xié)同優(yōu)化這些步驟,從而形成更好的芯片。整個(gè)晶圓廠也可以進(jìn)行孿生,以優(yōu)化整個(gè)工廠的運(yùn)營(yíng)。通過在這些不同層面創(chuàng)建數(shù)字孿生,SMART USA 的目標(biāo)是將美國(guó)芯片研發(fā)和制造成本降低 40% 以上,并將開發(fā)周期縮短 35% 以上。

SMART USA 研究所的主要舉措包括:

創(chuàng)建“數(shù)字骨干”——一個(gè)用于開發(fā)、測(cè)試和部署數(shù)字孿生的國(guó)家級(jí)平臺(tái)。

建立行業(yè)標(biāo)準(zhǔn),以確保數(shù)字孿生開發(fā)和使用的互操作性、安全性和一致性。

建立一個(gè)由晶圓廠、封裝、組裝和測(cè)試中心組成的國(guó)家級(jí)共享設(shè)施網(wǎng)絡(luò),以支持應(yīng)用研究。

推出一個(gè)數(shù)字市場(chǎng),供各組織共享和交流數(shù)字孿生技術(shù)、數(shù)據(jù)和最佳實(shí)踐。

通過課程開發(fā)和培訓(xùn),擴(kuò)大具備數(shù)字孿生能力的勞動(dòng)力隊(duì)伍,利用數(shù)字孿生技術(shù)為超過10萬(wàn)名半導(dǎo)體工人做好準(zhǔn)備。

通過這些舉措,SMART USA 成員將為行業(yè)打造美國(guó)首個(gè)安全、經(jīng)過驗(yàn)證且可互操作的數(shù)字孿生庫(kù)。這些數(shù)字孿生庫(kù)將使人工智能和高性能計(jì)算能夠直接在晶圓廠車間集成,并促進(jìn)制造商、設(shè)備供應(yīng)商和供應(yīng)商之間的實(shí)時(shí)協(xié)作,從而打造一個(gè)更加敏捷、高效和創(chuàng)新的行業(yè)。

除了 2.85 億美元的聯(lián)邦資金外,SMART USA 還獲得了來自行業(yè)和學(xué)術(shù)合作伙伴超過 7 億美元的非約束性承諾,五年內(nèi)總投資超過 10 億美元。SMART USA 將聯(lián)合美國(guó)頂尖研究人員和創(chuàng)新機(jī)構(gòu),共同致力于打造強(qiáng)大、有競(jìng)爭(zhēng)力且可持續(xù)發(fā)展的國(guó)內(nèi)半導(dǎo)體制造生態(tài)系統(tǒng)。

計(jì)量:通過精度、驗(yàn)證和

數(shù)字資產(chǎn)實(shí)現(xiàn)創(chuàng)新

在芯片上圖案化更小特征的能力,以及將多個(gè)芯片堆疊在一起實(shí)現(xiàn)三維異構(gòu)集成的能力,有望提升半導(dǎo)體產(chǎn)品的性能。然而,鑒于行業(yè)對(duì)絕對(duì)精度的要求及其對(duì)誤差的極高容忍度,制造商依賴于快速、準(zhǔn)確、精確地表征新特征并評(píng)估其產(chǎn)品價(jià)值的能力。

例如,隨著特征尺寸的減小,我們工具的分辨率也必須降低,同時(shí)又不影響測(cè)量的保真度。此外,由于我們將多個(gè)元件堆疊在一起用于先進(jìn)封裝應(yīng)用,制造商必須能夠在將更多元件投入封裝之前驗(yàn)證結(jié)構(gòu)完整性和埋置界面處的粘附性等指標(biāo)。

半導(dǎo)體計(jì)量是一門測(cè)量芯片物理特性和電氣特性的科學(xué)。 CHIPS計(jì)量項(xiàng)目正在進(jìn)行一系列高影響力的投資,旨在提升行業(yè)對(duì)非破壞性工廠工藝以及實(shí)驗(yàn)室工藝開發(fā)和故障分析進(jìn)行關(guān)鍵測(cè)量的能力。

這些投資包括在NIST開發(fā)新工具功能的硬件項(xiàng)目,以及生成參考文獻(xiàn)、數(shù)據(jù)集和軟件庫(kù)等數(shù)字資產(chǎn)。為了實(shí)現(xiàn)《CHIPS法案》的最終目標(biāo),計(jì)量項(xiàng)目正在激勵(lì)大學(xué)、聯(lián)邦實(shí)驗(yàn)室的科學(xué)家、初創(chuàng)企業(yè)和企業(yè),在國(guó)內(nèi)推動(dòng)世界領(lǐng)先的測(cè)量科學(xué)發(fā)展。

贏得芯片創(chuàng)新的辦法

隨著半導(dǎo)體行業(yè)創(chuàng)新路徑的演變,美國(guó)的研究項(xiàng)目也必須隨之發(fā)展,才能在新的創(chuàng)新格局中引領(lǐng)潮流,并與全球挑戰(zhàn)者競(jìng)爭(zhēng)。聯(lián)邦研究項(xiàng)目歷來能帶來顯著的投資經(jīng)濟(jì)回報(bào),而正在實(shí)施的半導(dǎo)體研究項(xiàng)目有望推動(dòng)創(chuàng)新、提升競(jìng)爭(zhēng)力,并增強(qiáng)美國(guó)的經(jīng)濟(jì)和國(guó)家安全。

全球各地正在涌現(xiàn)出合作研究聯(lián)盟,以構(gòu)建加速下一代微電子技術(shù)發(fā)展所需的協(xié)同效應(yīng)。總而言之,芯片研發(fā)項(xiàng)目 (CHIPS) 正在努力為美國(guó)半導(dǎo)體行業(yè)打造基礎(chǔ)設(shè)施和能力,使其能夠參與全球競(jìng)爭(zhēng)所需的合作和技術(shù)開發(fā),并確保美國(guó)在未來技術(shù)領(lǐng)域的領(lǐng)先地位。為了滿足新興的創(chuàng)新范式,聯(lián)邦政府資助的半導(dǎo)體研究項(xiàng)目對(duì)于增強(qiáng)美國(guó)半導(dǎo)體行業(yè)競(jìng)爭(zhēng)力的整體戰(zhàn)略仍然至關(guān)重要。

隨著這些項(xiàng)目在初步進(jìn)展的基礎(chǔ)上不斷發(fā)展,它們必須確保:

持續(xù)響應(yīng)行業(yè)優(yōu)先事項(xiàng);

建立一系列面向大批量生產(chǎn)的項(xiàng)目;

明確研究議程,以提升美國(guó)在整個(gè)行業(yè)的競(jìng)爭(zhēng)力;以及

相互協(xié)調(diào),確保工作協(xié)調(diào)一致。

這些項(xiàng)目開局良好,與行業(yè)進(jìn)一步合作將確保它們兌現(xiàn)推動(dòng)美國(guó)半導(dǎo)體創(chuàng)新的承諾。

附錄一:國(guó)家先進(jìn)封裝制造計(jì)劃

(NAPMP) 項(xiàng)目描述

NAPMP 圍繞六大研發(fā)重點(diǎn)和一個(gè)集成設(shè)施構(gòu)建。以下概述了各重點(diǎn)領(lǐng)域及其對(duì)半導(dǎo)體創(chuàng)新的重要性:

1.材料和基板:

將來自不同晶圓的一組組件集成在一起,使其能夠協(xié)同運(yùn)行以處理計(jì)算工作負(fù)載,是一項(xiàng)艱巨的挑戰(zhàn)。理想情況下,這些組件不會(huì)作為一組離散元件運(yùn)行,而是作為一個(gè)單一系統(tǒng)運(yùn)行,組件之間的界限模糊且無關(guān)緊要。數(shù)據(jù)和電源必須能夠在不同組件之間快速高效地傳輸。中介層是一種基板,其具有高度的電氣互連、熱管理材料和結(jié)構(gòu)安裝硬件,這些硬件已沉積在基板上(玻璃、硅、有機(jī)),以便“芯片集”能夠更快速、更高效地集成。一般而言,連接不同組件的互連越多,組件之間的距離越“近”,這些組件就越能作為一個(gè)單一系統(tǒng)運(yùn)行。

2.設(shè)備、工具和工藝:

需要新的工廠工裝來準(zhǔn)備基板和中介層、安裝芯片/芯片集、在晶圓廠測(cè)量這些工藝以確保質(zhì)量、封裝這些新系統(tǒng)以及建立電氣連接。

3.供電和熱管理:

在傳統(tǒng)的二維封裝中,熱量通過芯片頂部散熱,但隨著芯片集堆疊在一起,通過芯片集頂部散熱已不再可行。為了防止芯片過熱,需要新的方法將廢熱從封裝中排出。

4.光子學(xué)和連接器:

傳統(tǒng)的半導(dǎo)體技術(shù)歷來以電子方式在整個(gè)系統(tǒng)中傳輸數(shù)據(jù)。然而,通過金屬線/連接器傳輸電子會(huì)產(chǎn)生大量廢熱,這可能會(huì)損壞組件。將數(shù)字電子信號(hào)轉(zhuǎn)換為模擬光子信號(hào)可以實(shí)現(xiàn)更快的數(shù)據(jù)傳輸(甚至可以同時(shí)通過單個(gè)連接器傳輸多個(gè)信號(hào)),而不會(huì)產(chǎn)生令人頭疼的熱量。這一進(jìn)步為先進(jìn)封裝帶來了重大機(jī)遇。

5.芯片集生態(tài)系統(tǒng):

隨著先進(jìn)封裝技術(shù)的發(fā)展,以及業(yè)界越來越擅長(zhǎng)將各種芯片集集成到一個(gè)封裝中,專用芯片集的開發(fā)將有更多機(jī)會(huì)在芯片集市場(chǎng)中競(jìng)爭(zhēng)。這些芯片集將涵蓋廣泛的用例和終端市場(chǎng)。

6.協(xié)同設(shè)計(jì)和電子設(shè)計(jì)自動(dòng)化 (EDA):

先進(jìn)封裝技術(shù)的出現(xiàn)顯著提升了設(shè)計(jì)自由度(例如堆疊、異構(gòu)集成和更大的封裝尺寸)以及新封裝的選擇。EDA 軟件必須隨之發(fā)展,以優(yōu)化這些新封裝的設(shè)計(jì)。

附錄二:國(guó)家半導(dǎo)體技術(shù)中心

(NSTC) 設(shè)施描述

NSTC 正在建設(shè)三個(gè)主要設(shè)施,以提供推進(jìn)大規(guī)模商業(yè)化技術(shù)試點(diǎn)和原型設(shè)計(jì)工作所需的基礎(chǔ)設(shè)施和能力。以下是每個(gè)設(shè)施的描述:

1. EUV 加速器

隨著先進(jìn)邏輯處理器和存儲(chǔ)器技術(shù)的特征尺寸不斷減小,業(yè)界開始在其本已冗長(zhǎng)的制造流程中增加更多步驟,以便能夠?qū)Ω〉木w管進(jìn)行圖案化(即多重圖案化光刻)。對(duì)于半導(dǎo)體制造商而言,這意味著在工廠生產(chǎn)過程中需要儲(chǔ)存更多庫(kù)存、添加工裝模塊、增加潔凈室面積以容納這些工具(這已經(jīng)是建造這些工具中最昂貴的建筑面積),以及需要更多技術(shù)人員和工程師來操作這些工具。而且,隨著制造流程步驟的增加,出錯(cuò)的可能性也隨之增加——在一個(gè)以精確和不容差錯(cuò)著稱的行業(yè)中——這會(huì)影響產(chǎn)量和盈利能力。 EUV 光刻技術(shù)的發(fā)展顯著減少了對(duì)多重圖案化的需求,簡(jiǎn)化了制造流程,并提高了即使是最小特征尺寸的良率,最終有助于提供更先進(jìn)的芯片并實(shí)現(xiàn)企業(yè)可持續(xù)發(fā)展。

為了使行業(yè)能夠跟上摩爾定律的步伐,制造出越來越小的晶體管特征,EUV 光刻技術(shù)的持續(xù)進(jìn)步至關(guān)重要。同時(shí),支持光刻技術(shù)的相關(guān)行業(yè)也必須同步推進(jìn)其技術(shù)發(fā)展。例如,必須開發(fā)能夠提供納米(甚至亞納米)長(zhǎng)度尺度分辨率的新型光刻膠。一旦光刻膠開發(fā)完成,工具制造商必須設(shè)計(jì)出如何在晶圓表面非常均勻且薄地沉積新型光刻膠的技術(shù)。最后,計(jì)量公司需要弄清楚如何以行業(yè)要求的精度來測(cè)量所有這些參數(shù)。NSTC EUV 加速器將發(fā)揮關(guān)鍵作用,支持整個(gè)行業(yè)共同開發(fā)創(chuàng)新,并將新的 EUV 技術(shù)推向市場(chǎng)。

EUV加速器將落戶奧爾巴尼納米技術(shù)中心,該中心將成為北美唯一一家擁有高數(shù)值孔徑 (NA) EUV光刻技術(shù)的公共研究中心。高數(shù)值孔徑 EUV 光刻技術(shù)的標(biāo)價(jià)約為 3.5 億美元,是實(shí)現(xiàn)尖端處理器圖案化的關(guān)鍵和先進(jìn)制造工具。NSTC 將通過這項(xiàng)前所未有的工具實(shí)現(xiàn)普及,為眾多美國(guó)初創(chuàng)企業(yè)提供寶貴的使用渠道,助力其在國(guó)內(nèi)市場(chǎng)建立領(lǐng)導(dǎo)地位。此外,安置和維護(hù)這樣的工具成本高昂。將 EUV 加速器落戶該中心,NSTC 找到了一種降低資本支出和加速此類資源利用的重要途徑。負(fù)責(zé)運(yùn)營(yíng)該中心的紐約州創(chuàng)新與技術(shù)中心 (NY CREATES) 預(yù)計(jì)將從 NSTC 獲得 8.25 億美元資金。該設(shè)施計(jì)劃于 2025 年夏季投入運(yùn)營(yíng)。

2. 設(shè)計(jì)與協(xié)作設(shè)施

確定晶圓上數(shù)十億個(gè)晶體管的布局以執(zhí)行復(fù)雜的計(jì)算工作負(fù)載是一項(xiàng)極其復(fù)雜的任務(wù)。半導(dǎo)體價(jià)值鏈的設(shè)計(jì)環(huán)節(jié)包括開發(fā)電子設(shè)計(jì)自動(dòng)化 (EDA) 軟件的公司、組裝設(shè)計(jì)模塊庫(kù)以用于芯片設(shè)計(jì)的 IP 提供商,以及使用 EDA 軟件和 IP 模塊設(shè)計(jì)完整芯片系統(tǒng)的無晶圓廠公司。此外,該行業(yè)環(huán)節(jié)處于硬件提供商和軟件提供商之間的紐帶,對(duì)全棧創(chuàng)新至關(guān)重要。

NSTC 設(shè)計(jì)與協(xié)作設(shè)施將支持設(shè)計(jì)研發(fā),并配備一個(gè)全新的“設(shè)計(jì)使能網(wǎng)關(guān)”,通過集中訪問 EDA 軟件和數(shù)據(jù)庫(kù),降低芯片初創(chuàng)企業(yè)的門檻。通過利用 NSTC 及其成員的集體購(gòu)買力,DCF 將加快研發(fā)進(jìn)度,并顯著降低與實(shí)驗(yàn)芯片和架構(gòu)的設(shè)計(jì)和開發(fā)相關(guān)的不斷增長(zhǎng)的成本。該設(shè)施還將成為國(guó)家半導(dǎo)體技術(shù)中心(NSTC)人才卓越中心的核心。該中心將投資2.5億美元,用于培養(yǎng)不同教育水平和學(xué)科的半導(dǎo)體人才(包括技術(shù)人員、工程師和研究人員),以解決芯片行業(yè)預(yù)計(jì)出現(xiàn)的人才短缺問題。這座由Natcast運(yùn)營(yíng)的設(shè)施還將容納NSTC的核心行政職能,該設(shè)施位于硅谷中心地帶,預(yù)計(jì)將于2025年投入運(yùn)營(yíng)。

3. 原型設(shè)計(jì)和先進(jìn)封裝試點(diǎn)設(shè)施

NSTC還將在最先進(jìn)的研發(fā)環(huán)境中,將新技術(shù)擴(kuò)展到商業(yè)應(yīng)用,并促進(jìn)新材料、器件和先進(jìn)封裝解決方案從實(shí)驗(yàn)室到工廠的轉(zhuǎn)型。新技術(shù)通常始于學(xué)術(shù)領(lǐng)域,并以相對(duì)較小的規(guī)模和較低的產(chǎn)量進(jìn)行演示。概念驗(yàn)證完成后,必須進(jìn)行大量的開發(fā)工作,使技術(shù)成熟,然后才能進(jìn)入市場(chǎng)。例如,在半導(dǎo)體設(shè)備中,晶圓的均勻性、批次一致性、生產(chǎn)率以及許多其他問題都必須經(jīng)過優(yōu)化,才能將設(shè)備視為“成熟”。同時(shí),新技術(shù)為晶圓帶來的價(jià)值必須與市場(chǎng)愿意支付的價(jià)格相協(xié)調(diào)。研發(fā)團(tuán)隊(duì)必須解決科學(xué)和經(jīng)濟(jì)問題,才能證明新技術(shù)的合理性。通常,如果不將晶圓送入完整的集成制造流程并測(cè)量其整體性能,就無法正確評(píng)估其價(jià)值。

原型設(shè)計(jì)和先進(jìn)封裝中試設(shè)施將提供開發(fā)和擴(kuò)展技術(shù)以實(shí)現(xiàn)商業(yè)價(jià)值的能力,并將容納完整的集成制造流程,以便對(duì)技術(shù)進(jìn)行充分驗(yàn)證。該設(shè)施將位于亞利桑那州立大學(xué)研究園區(qū)。亞利桑那州立大學(xué)的初步活動(dòng)將于2026年開始,新設(shè)施的建設(shè)將于2028年底完工并投入運(yùn)營(yíng)。盡管仍有大量工作要做,但NSTC已經(jīng)吸引了近150家成員,其中包括領(lǐng)先的芯片公司和大學(xué),并有望在未來幾年成為美國(guó)領(lǐng)先的半導(dǎo)體研究聯(lián)盟之一。